XC6SLX75-2FGG484C programuojamų vartų masyvas

♠ Produkto aprašymas

| Produkto atributas | Atributo vertė |

| Gamintojas: | Xilinx |

| Produkto kategorija: | FPGA – lauke programuojamų vartų masyvas |

| RoHS: | Detalės |

| Serija: | XC6SLX75 |

| Loginių elementų skaičius: | 74637 LE |

| I/O skaičius: | 280 I/O |

| Maitinimo įtampa – min.: | 1,14 V |

| Maitinimo įtampa – maks.: | 1,26 V |

| Minimali darbinė temperatūra: | 0 C |

| Maksimali darbinė temperatūra: | +85 C |

| Duomenų perdavimo sparta: | - |

| Siųstuvų-imtuvų skaičius: | - |

| Montavimo stilius: | SMD/SMT |

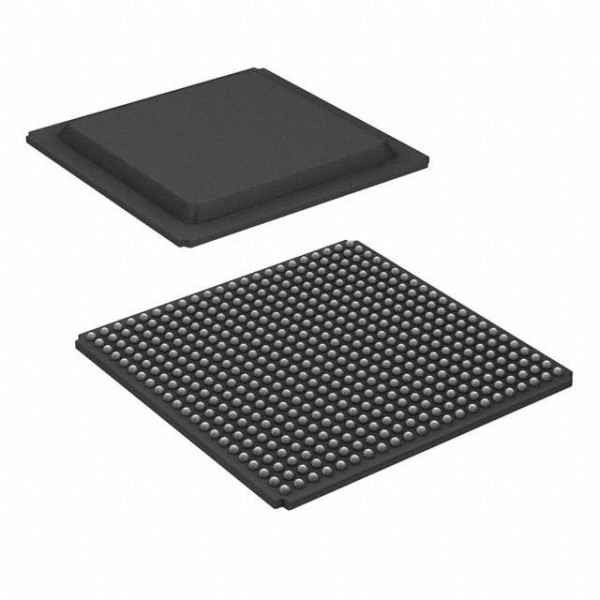

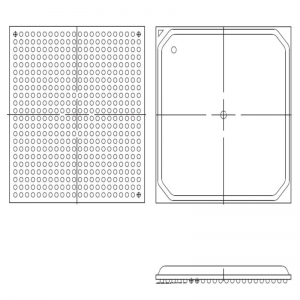

| Pakuotė / dėklas: | FCBGA-484 |

| Prekinis ženklas: | Xilinx |

| Paskirstyta RAM: | 692 kbit |

| Įdėtasis blokinis RAM – EBR: | 3096 kbit |

| Maksimalus veikimo dažnis: | 1080 MHz |

| Jautrus drėgmei: | Taip |

| Loginių masyvo blokų skaičius – LAB: | 5831 LAB |

| Darbinė maitinimo įtampa: | 1,2 V |

| Produkto tipas: | FPGA – lauke programuojamų vartų masyvas |

| Gamyklos pakuotės kiekis: | 1 |

| Subkategorija: | Programuojami loginiai IC |

| Prekinis pavadinimas: | spartietiškas |

| Vieneto svoris: | 1,662748 uncijos |

♠ „Spartan-6“ šeimos apžvalga

Spartan®-6 šeima suteikia pirmaujančias sistemos integravimo galimybes su mažiausiomis bendromis didelės apimties programomis.Trylikos narių šeima užtikrina didesnį tankį nuo 3 840 iki 147 443 loginių elementų, sunaudoja perpus mažiau energijos nei ankstesnės Spartan šeimos, ir greitesnį bei išsamesnį ryšį.Sukurta pagal brandžią 45 nm mažos galios vario proceso technologiją, užtikrinančią optimalų kainos, galios ir našumo balansą, Spartan-6 šeima siūlo naują, efektyvesnę dviejų registrų 6 įvesties paieškos lentelės (LUT) logiką ir gausus įmontuotų sistemos lygio blokų pasirinkimas.Tai apima 18 Kb (2 x 9 Kb) blokų RAM, antros kartos DSP48A1 skilteles, SDRAM atminties valdiklius, patobulintus mišraus režimo laikrodžių valdymo blokus, SelectIO™ technologiją, optimizuotus didelės spartos nuosekliųjų siųstuvų-imtuvų blokus, su PCI Express® suderinamus Endpoint blokus, pažangius sistemos lygio energijos valdymo režimai, automatinio aptikimo konfigūracijos parinktys ir patobulinta IP sauga su AES ir įrenginio DNR apsauga.

Šios funkcijos suteikia nebrangią programuojamą alternatyvą pasirinktiniams ASIC gaminiams su precedento neturinčiu paprastu naudojimu.Spartan-6 FPGA siūlo geriausią sprendimą didelės apimties loginiams projektams, į vartotoją orientuotam DSP dizainui ir ekonomiškai jautrioms įterptoms programoms.Spartan-6 FPGA yra programuojamas silicio pagrindas tikslinėms projektavimo platformoms, kurios tiekia integruotus programinės ir techninės įrangos komponentus, leidžiančius dizaineriams sutelkti dėmesį į naujoves, kai tik prasideda jų kūrimo ciklas.

• Spartan-6 šeima:

- Spartan-6 LX FPGA: optimizuota logika

- Spartan-6 LXT FPGA: didelės spartos nuoseklusis ryšys

• Sukurta pigiai

- Daug efektyvių integruotų blokų

- Optimizuotas I/O standartų pasirinkimas

- Pastatytos pagalvėlės

- Didelės apimties plastiko viela surištos pakuotės

• Maža statinė ir dinaminė galia

- 45 nm procesas optimizuotas sąnaudoms ir mažai galiai

- Hibernate maitinimo išjungimo režimas nulinės energijos

- Sustabdymo režimas palaiko būseną ir konfigūraciją su kelių kontaktų pažadinimo ir valdymo patobulinimu

- Mažesnės galios 1,0 V šerdies įtampa (tik LX FPGA, tik -1 l)

- Aukštos kokybės 1,2 V šerdies įtampa (LX ir LXT FPGA, -2, -3 ir -3N greičio klasės)

• Kelių įtampos, kelių standartų SelectIO™ sąsajos bankai

- Iki 1080 Mb/s duomenų perdavimo sparta vienam diferencialiniam I/O

- Pasirenkama išvesties pavara, iki 24 mA vienam kaiščiui

- Nuo 3,3 V iki 1,2 VI/O standartai ir protokolai

- Nebrangios HSTL ir SSTL atminties sąsajos

- Karšto apsikeitimo laikymasis

- Reguliuojami įvesties / išvesties sukimosi dažniai, siekiant pagerinti signalo vientisumą

• Didelės spartos GTP serijiniai siųstuvai-imtuvai LXT FPGA

- Iki 3,2 Gb/s

- Didelės spartos sąsajos, įskaitant: Serial ATA, Aurora, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort ir XAUI

• Integruotas galinio taško blokas PCI Express projektams (LXT)

• Pigios PCI® technologijos palaikymas, suderinamas su 33 MHz, 32 ir 64 bitų specifikacijomis.

• Efektyvios DSP48A1 skiltys

- Didelio našumo aritmetika ir signalų apdorojimas

- Greitas 18 x 18 daugiklis ir 48 bitų akumuliatorius

- Vamzdynų ir kaskados galimybė

- Išankstinis priedas, padedantis taikyti filtrą

• Integruoti atminties valdiklio blokai

- DDR, DDR2, DDR3 ir LPDDR palaikymas

- Duomenų perdavimo sparta iki 800 Mb/s (12,8 Gb/s didžiausias pralaidumas)

- Kelių prievadų magistralės struktūra su nepriklausomu FIFO, siekiant sumažinti projektavimo laiko problemas

• Gausūs loginiai ištekliai su padidintu loginiu pajėgumu

- Pasirenkamas pamainų registras arba paskirstytos RAM palaikymas

- Veiksmingi 6 įėjimų LUT pagerina našumą ir sumažina galią

- LUT su dvigubais šliaužtinukais, skirtais vamzdynams

• Blokuokite RAM naudodami platų detalumo diapazoną

- Greitas RAM blokavimas su baitų rašymo įgalinimu

- 18 Kb blokai, kuriuos pasirinktinai galima užprogramuoti kaip dvi nepriklausomas 9 Kb blokų RAM

• Laikrodžio valdymo plytelė (CMT), skirta geresniam veikimui

- Mažas triukšmas, lankstus laikrodis

- Skaitmeninių laikrodžių tvarkyklės (DCM) pašalina laikrodžio perkrypimą ir darbo ciklo iškraipymus

- Fazės užblokuotos kilpos (PLL), skirtos mažo virpėjimo laikrodžiui

- Dažnio sintezė vienu metu dauginant, dalijant ir keičiant fazes

- Šešiolika žemo iškrypimo pasaulinių laikrodžių tinklų

• Supaprastinta konfigūracija, palaiko žemų sąnaudų standartus

- 2 kontaktų automatinio aptikimo konfigūracija

- Platus trečiųjų šalių SPI (iki x4) ir NOR blykstės palaikymas

- „Xilinx“ platformos blykstė su JTAG

- „MultiBoot“ palaikymas nuotoliniam atnaujinimui naudojant kelis bitų srautus, naudojant „watchdog“ apsaugą

• Padidintas dizaino apsaugos saugumas

- Unikalus įrenginio DNR identifikatorius, skirtas dizaino autentifikavimui

- AES bitų srauto šifravimas didesniuose įrenginiuose

• Greitesnis integruotas apdorojimas su patobulintu, pigiu, minkštu MicroBlaze™ procesoriumi

• Pramonėje pirmaujantis IP ir etaloninis dizainas