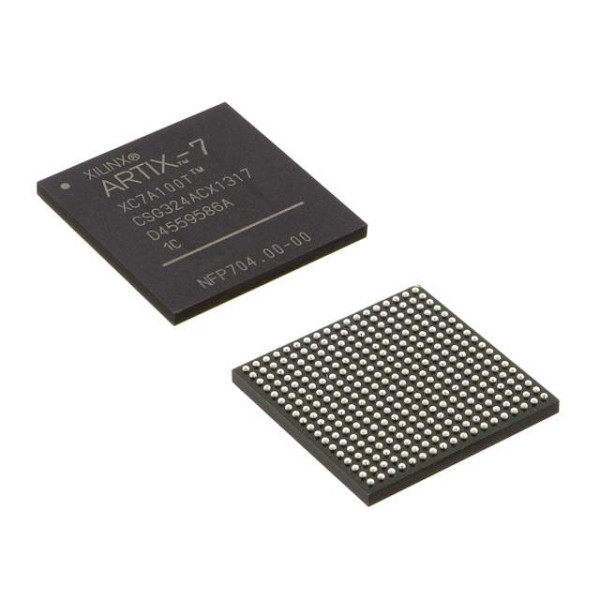

XC7A50T-2CSG324I FPGA – Lauko programuojama loginių elementų matrica XC7A50T-2CSG324I

♠ Produkto aprašymas

| Produkto atributas | Atributo reikšmė |

| Gamintojas: | Xilinx |

| Produkto kategorija: | FPGA - lauko programuojamas vartų masyvas |

| Serija: | XC7A50T |

| Loginių elementų skaičius: | 52160 LE |

| Įvesčių / išvesčių skaičius: | 210 įėjimų/išėjimų |

| Maitinimo įtampa - Min.: | 0,95 V |

| Maitinimo įtampa - maks.: | 1,05 V |

| Minimali darbinė temperatūra: | - 40 °C |

| Maksimali darbinė temperatūra: | + 100 °C |

| Duomenų perdavimo sparta: | - |

| Siųstuvų-imtuvų skaičius: | - |

| Montavimo stilius: | SMD/SMT |

| Pakuotė / dėklas: | CSBGA-324 |

| Prekės ženklas: | Xilinx |

| Paskirstyta RAM: | 600 kbit/s |

| Įterptoji blokinė RAM – EBR: | 2700 kbit/s |

| Jautrus drėgmei: | Taip |

| Loginių masyvų blokų skaičius – LAB: | 4075 LAB |

| Darbinė maitinimo įtampa: | 1 V |

| Produkto tipas: | FPGA - lauko programuojamas vartų masyvas |

| Gamyklinės pakuotės kiekis: | 1 |

| Subkategorija: | Programuojamos loginės integrinės grandinės |

| Prekinis pavadinimas: | Artix |

| Vieneto svoris: | 1 uncija |

♠ „Xilinx® 7“ serijos FPGA sudaro keturios FPGA šeimos, kurios patenkina visą sistemos reikalavimų spektrą – nuo mažos kainos, mažo formato, jautrių kainai, didelio našumo programų iki itin didelio našumo ryšio pralaidumo, loginių pajėgumų ir signalo apdorojimo galimybių, skirtų reikliausioms didelio našumo programoms.

„Xilinx®“ 7 serijos FPGA sudaro keturios FPGA šeimos, kurios patenkina visą sistemos reikalavimų spektrą – nuo mažos kainos, mažo formato, jautrių sąnaudoms, didelio našumo programų iki itin didelio jungiamumo pralaidumo, loginių pajėgumų ir signalo apdorojimo galimybių, skirtų reikliausioms didelio našumo programoms. 7 serijos FPGA apima:

• „Spartan®-7“ šeima: optimizuota mažai kainai, mažiausiam energijos suvartojimui ir dideliam įvesties/išvesties našumui. Galima įsigyti nebrangioje, labai mažo formato pakuotėje, kad būtų mažiausias spausdintinės plokštės dydis.

• „Artix®-7“ šeima: optimizuota mažos galios taikymams, kuriems reikalingi nuoseklieji siųstuvai-imtuvai ir didelis DSP bei loginis pralaidumas. Užtikrina mažiausią bendrą medžiagų kainą didelio pralaidumo, sąnaudoms jautrioms taikymams.

• „Kintex®-7“ šeima: optimizuota geriausiam kainos ir kokybės santykiui, dvigubai geresnė, palyginti su ankstesne karta, todėl galima sukurti naują FPGA klasę.

• „Virtex®-7“ šeima: optimizuota didžiausiam sistemos našumui ir talpai, dvigubai padidinus sistemos našumą. Didžiausio pajėgumo įrenginiai, kuriuos įgalina sluoksniuotos silicio jungčių (SSI) technologija.

Sukurti naudojant pažangiausią, didelio našumo, mažo energijos suvartojimo (HPL), 28 nm, didelio k metalinių vartų (HKMG) proceso technologiją, 7 serijos FPGA leidžia neprilygstamai padidinti sistemos našumą – 2,9 Tb/s įvesties/išvesties pralaidumą, 2 milijonų loginių elementų talpą ir 5,3 TMAC/s DSP, tuo pačiu sunaudojant 50 % mažiau energijos nei ankstesnės kartos įrenginiai, ir siūlo visiškai programuojamą alternatyvą ASSP ir ASIC.

• Pažangi didelio našumo FPGA logika, pagrįsta realia 6 įėjimų paieškos lentelės (LUT) technologija, konfigūruojama kaip paskirstyta atmintis.

• 36 Kb dviejų prievadų blokinė RAM su integruota FIFO logika duomenų buferizavimui luste.

• Didelio našumo „SelectIO™“ technologija, palaikanti DDR3 sąsajas iki 1866 Mb/s.

• Didelės spartos nuoseklusis ryšys su integruotais kelių gigabitų siųstuvais-imtuvais nuo 600 Mb/s iki maks. 6,6 Gb/s greičio, iki 28,05 Gb/s, siūlant specialų mažos energijos sąnaudos režimą, optimizuotą lustų tarpusavio sąsajoms.

• Vartotojo konfigūruojama analoginė sąsaja (XADC), apimanti dvigubus 12 bitų 1MSPS analoginius-skaitmeninius keitiklius su integruotais terminiais ir maitinimo jutikliais.

• DSP griežinėliai su 25 x 18 daugikliu, 48 bitų kaupikliu ir išankstiniu sumatoriumi, skirtu didelio našumo filtravimui, įskaitant optimizuotą simetrinio koeficiento filtravimą.

• Galingos laikrodžių valdymo plytelės (CMT), derinančios fazės fiksavimo kilpos (PLL) ir mišraus režimo laikrodžių valdymo (MMCM) blokus, užtikrinančius didelį tikslumą ir mažą virpėjimą.

• Greitai diegkite įterptuosius apdorojimo procesus naudodami „MicroBlaze™“ procesorių.

• Integruotas PCI Express® (PCIe) blokas, skirtas iki x8 Gen3 galinių taškų ir šakninių prievadų konstrukcijoms.

• Platus konfigūravimo parinkčių pasirinkimas, įskaitant palaikymą įprastiems atminties elementams, 256 bitų AES šifravimą su HMAC/SHA-256 autentifikavimu ir integruotą SEU aptikimą bei taisymą.

• Pigus, vielinio sujungimo, bekontaktis „flip-chip“ ir didelio signalo vientisumo „flip-chip“ korpusas, leidžiantis lengvai perkelti duomenis tarp šeimos narių tame pačiame korpuse. Visi korpusai galimi be švino, o kai kurie – su švino parinktimi.

• Sukurtas dideliam našumui ir mažiausiam energijos suvartojimui, naudojant 28 nm, HKMG, HPL procesą, 1,0 V šerdies įtampos proceso technologiją ir 0,9 V šerdies įtampos parinktį dar mažesnei energijos suvartojimui.