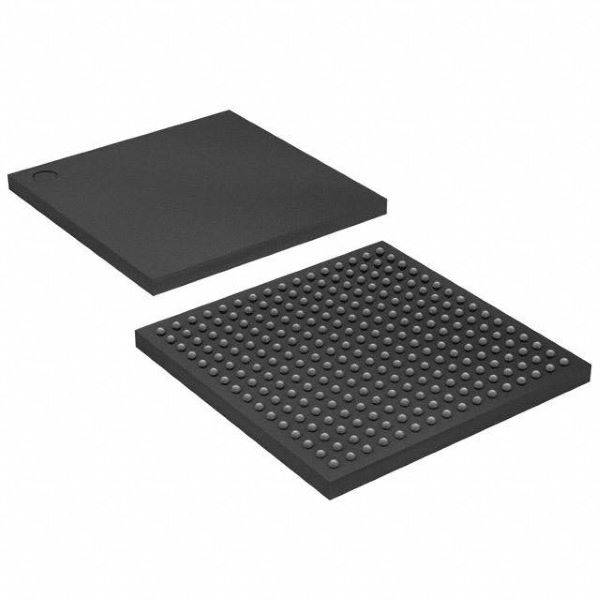

XC6SLX25-2FTG256C FPGA – lauko programuojama loginių elementų matrica. Šiuo metu gamykla nepriima šio produkto užsakymų.

♠ Produkto aprašymas

| Produkto atributas | Atributo reikšmė |

| Gamintojas: | Xilinx |

| Produkto kategorija: | FPGA - lauko programuojamas vartų masyvas |

| RoHS: | Išsami informacija |

| Serija: | XC6SLX25 |

| Loginių elementų skaičius: | 24051 LE |

| Įvesčių / išvesčių skaičius: | 186 įvesties/išvesties |

| Maitinimo įtampa - Min.: | 1,14 V |

| Maitinimo įtampa - maks.: | 1,26 V |

| Minimali darbinė temperatūra: | 0 °C |

| Maksimali darbinė temperatūra: | + 85 °C |

| Duomenų perdavimo sparta: | - |

| Siųstuvų-imtuvų skaičius: | - |

| Montavimo stilius: | SMD/SMT |

| Pakuotė/dėklas: | FBGA-256 |

| Prekės ženklas: | Xilinx |

| Paskirstyta RAM: | 229 kbit/s |

| Įterptoji blokinė RAM – EBR: | 936 kbit/s |

| Maksimalus veikimo dažnis: | 1080 MHz |

| Jautrus drėgmei: | Taip |

| Loginių masyvų blokų skaičius – LAB: | 1879 m. LAB |

| Darbinė maitinimo įtampa: | 1,2 V |

| Produkto tipas: | FPGA - lauko programuojamas vartų masyvas |

| Gamyklinės pakuotės kiekis: | 1 |

| Subkategorija: | Programuojamos loginės integrinės grandinės |

| Prekinis pavadinimas: | Spartietis |

| Vieneto svoris: | 21,576 g |

♠ „Spartan-6“ šeimos apžvalga

„Spartan®-6“ šeima suteikia pirmaujančias sistemų integravimo galimybes už mažiausią bendrą kainą didelio masto programoms. Trylikos narių šeima pasižymi padidintu tankiu – nuo 3 840 iki 147 443 loginių elementų, sunaudoja perpus mažiau energijos nei ankstesnės „Spartan“ šeimos, o jungiamumas yra greitesnis ir platesnis. Sukurta naudojant brandžią 45 nm mažos galios vario proceso technologiją, užtikrinančią optimalų kainos, galios ir našumo balansą, „Spartan-6“ šeima siūlo naują, efektyvesnę, dviejų registrų 6 įėjimų paieškos lentelės (LUT) logiką ir platų integruotų sistemos lygio blokų pasirinkimą. Tai apima 18 Kb (2 x 9 Kb) blokų RAM, antros kartos DSP48A1 skilteles, SDRAM atminties valdiklius, patobulintus mišraus režimo laikrodžio valdymo blokus, „SelectIO™“ technologiją, energijos taupymui optimizuotus didelės spartos nuosekliojo siųstuvo-imtuvo blokus, su PCI Express® suderinamus galinių taškų blokus, pažangius sistemos lygio energijos valdymo režimus, automatinio aptikimo konfigūracijos parinktis ir patobulintą IP saugumą su AES ir įrenginio DNR apsauga. Šios savybės suteikia nebrangią programuojamą alternatyvą individualiems ASIC gaminiams, pasižyminčią precedento neturinčiu naudojimo paprastumu. „Spartan-6 FPGA“ siūlo geriausią sprendimą didelio masto loginiams projektams, į vartotoją orientuotiems DSP projektams ir jautrioms sąnaudoms įterptosioms programoms. „Spartan-6 FPGA“ yra programuojamas silicio pagrindas tikslinėms projektavimo platformoms, kurios teikia integruotus programinės ir aparatinės įrangos komponentus, leidžiančius projektuotojams sutelkti dėmesį į inovacijas vos prasidėjus jų kūrimo ciklui.

• „Spartan-6“ šeima:

• „Spartan-6 LX FPGA“: optimizuota logikai

• „Spartan-6 LXT FPGA“: didelės spartos nuoseklusis ryšys

• Sukurta atsižvelgiant į mažą kainą

• Keli efektyvūs integruoti blokai

• Optimizuotas įvesties / išvesties standartų pasirinkimas

• Pakopomis išdėstyti pagalvėlės

• Didelio tūrio plastikiniai vieliniai paketai

• Maža statinė ir dinaminė galia

• 45 nm procesas, optimizuotas atsižvelgiant į kainą ir mažą energijos suvartojimą

• Hibernacijos išjungimo režimas, kad energijos sąnaudos būtų nulinės

• Sustabdymo režimas palaiko būseną ir konfigūraciją su kelių kontaktų pažadinimu ir valdymo patobulinimu

• Mažesnės galios 1,0 V šerdies įtampa (tik LX FPGA, -1L)

• Didelio našumo 1,2 V pagrindinė įtampa (LX ir LXT FPGA, -2, -3 ir -3N greičio klasės)

• Įvairių įtampų, kelių standartų „SelectIO™“ sąsajų blokai

• Iki 1080 Mb/s duomenų perdavimo sparta vienam diferencialiniam įėjimui/išėjimui

• Pasirenkamas išėjimo valdiklis, iki 24 mA vienam kontaktui

• 3,3 V iki 1,2 VI/O standartai ir protokolai

• Pigios HSTL ir SSTL atminties sąsajos

• Atitiktis karštojo keitimo sistemoms

• Reguliuojami įvesties / išvesties pokyčio dažniai, siekiant pagerinti signalo vientisumą

• Didelės spartos GTP nuoseklieji siųstuvai-imtuvai LXT FPGA mikroschemose

• Iki 3,2 Gb/s

• Didelės spartos sąsajos, įskaitant: nuoseklųjį ATA, „Aurora“, 1G Ethernet, PCI Express, OBSAI, CPRI, EPON, GPON, DisplayPort ir XAUI

• Integruotas galinių taškų blokas, skirtas PCI Express modeliams (LXT)

• Palaikoma nebrangi PCI® technologija, suderinama su 33 MHz, 32 ir 64 bitų specifikacija.

• Efektyvios DSP48A1 skiltelės

• Didelio našumo aritmetinis ir signalų apdorojimas

• Greitas 18 x 18 daugiklis ir 48 bitų akumuliatorius

• Vamzdynų ir kaskadų galimybė

• Išankstinis sumatorius, padedantis taikyti filtrą

• Integruoti atminties valdiklio blokai

• Palaiko DDR, DDR2, DDR3 ir LPDDR atmintis

• Duomenų perdavimo sparta iki 800 Mb/s (didžiausias pralaidumas 12,8 Gb/s)

• Daugiaportė magistralės struktūra su nepriklausomu FIFO, siekiant sumažinti projektavimo laiko problemas

• Gausūs loginiai ištekliai su padidinta loginio pajėgumo

• Papildomas poslinkio registro arba paskirstytos RAM palaikymas

• Efektyvios 6 įėjimų LUT lentelės pagerina našumą ir sumažina energijos sąnaudas

• LUT su dviem trigeriais, skirtais vamzdynų pagrindu veikiančioms programoms

• Blokuoti RAM su plačiu detalumo diapazonu

• Greita blokinė RAM su baitų įrašymo įgalinimu

• 18 Kb blokai, kuriuos pasirinktinai galima programuoti kaip dvi nepriklausomas 9 Kb blokų RAM atmintis

• Laikrodžio valdymo plytelė (CMT) pagerintam našumui

• Mažas triukšmo lygis, lankstus takto signalas

• Skaitmeniniai laikrodžių valdikliai (DCM) pašalina laikrodžio iškraipymus ir darbo ciklo iškraipymus

• Fazės fiksavimo kilpos (PLL) mažo virpesių lygio taktiniam signalui

• Dažnio sintezė su vienalaikiu dauginimu, dalymu ir fazės poslinkiu

• Šešiolika mažo iškreipimo pasaulinių laikrodžių tinklų

• Supaprastinta konfigūracija, palaiko pigius standartus

• 2 kontaktų automatinio aptikimo konfigūracija

• Platus trečiųjų šalių SPI (iki x4) ir NOR blykstės palaikymas

• Funkcijomis turtinga „Xilinx Platform Flash“ su JTAG

• „MultiBoot“ palaikymas nuotoliniam atnaujinimui su keliais bitų srautais, naudojant stebėjimo apsaugą

• Patobulinta dizaino apsauga

• Unikalus įrenginio DNR identifikatorius dizaino autentifikavimui

• AES bitų srauto šifravimas didesniuose įrenginiuose

• Greitesnis integruotas apdorojimas naudojant patobulintą, nebrangų „MicroBlaze™“ programinę įrangą

• Pramonėje pirmaujantys intelektinės nuosavybės ir etaloniniai dizainai